# Crystal Clear Technology

## **Product Specification**

**G2432x30xxxxx**

(with controller: S1D13700)

(4.7 INCH QVGA SERIES)

## Crystal Clear Technology sdn. bhd.

16Jalan TP5—Taman Perindustrian Sime UEP 47600 Subang Jaya—Selangor DE Malaysia. T: +603 80247099 F: +603 80247098

Spec. No: G2432x30xxxxx REV 2.0

| 1.0 | Table of Contents                        | Page    |

|-----|------------------------------------------|---------|

| 1.  | Table of Contents                        | 1       |

| 2.  | Record of revision                       | 2       |

| 3.  | General specification                    | 3       |

| 4.  | Absolute maximum ratings                 | 4       |

| 5.  | Electrical characteristics               | 4       |

| 6.  | Environmental requirement                | 4       |

| 7.  | LCD specification                        | 5 ~ 7   |

| 8.  | Interface                                | 8       |

| 9.  | Timing characteristics / Timing diagrams | 9 ~ 16  |

| 10. | . Power Supply                           | 17      |

| 11. | . Block Diagram                          | 17      |

| 12. | . Quality Assurance                      | 18~ 20  |

| 13. | . Precaution of Using LCM                | 21 ~ 22 |

| 14. | . Outline Drawing                        | 23      |

#### 2.0 Record of revision

| Rev | Date     | Item | Page | Comment                     | Originator | Checked By |

|-----|----------|------|------|-----------------------------|------------|------------|

| 1.0 | 10/04/10 |      |      | Initial Release             | Khairiah   | Azhar      |

| 2.0 | 23/07/10 | 5.1  | 4    | Add backlight option - CCFL | Khairiah   | Azhar      |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

|     |          |      |      |                             |            |            |

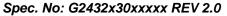

3.0 General specification

Display format: Graphics, 240 (H) x 320 (W)

Pixel size: 0.28 (H) x 0.28 (W) mm Pixel pitch: 0.30 (H) x 0.30 (W) mm

View area: 80.0 (H) x 105.0 (W) mm

Active area: 72.00 (H) x 95.98 (W) mm

General dimensions: 96.8 (H) x 143.0 (W) x 10.0 max (T) mm

Driver: NT7086 or equivalent

Controller: S1D13700F00

X 3 || 0 | |X||X||X||X||G 3 MODEL NUMBER STD. GRAPHIC: No. of row followed by no. of column **BACKLIGHT MODE** W : Side Led Backlight (White) B: Side Led Backlight (Blue) G: Side Led Backlight (Green) C: CCFL Backlight (white) N: No Backlight **DISPLAY MODE** B: Black White (FSTN) N : Negative (FSTN) Blue (Single Retardation ) U : Negative (FSTN) Black/White (Double Retardation ) L: Negative (STN) Blue VIEWING ANGLE T: Top view (12 O'clock) B: Bottom view (6 O'clock) **OPERATING TEMPERATURE** N : Normal Temperature ( 0°C to +50°C ) W: Wide Temperature ( -20°C to +70°C) POLARIZER OPTION 0 : Transflective Back Polarizer 1: Transmissive Back Polarizer DC-DC OPTION 0 : Without DC-DC on Board 1: With DC-DC on Board Additional Character for Semi-Customise (Minor Changes from Standard Model Refer to factory for other versions. Term and Condition apply

Spec. No: G2432x30xxxxx REV 2.0

#### 4.0 Absolute maximum rating (at Vss = 0V, ambient temperature = 25°C)

| NO | ITEM                              | SIMBOL                              | MIN          | MAX   | UNIT |

|----|-----------------------------------|-------------------------------------|--------------|-------|------|

| 1. | Power Supply voltage (Logic)      | $V_{\mathrm{DD}} - V_{\mathrm{SS}}$ | 0            | 7.0   | V    |

| 2. | Power Supply voltage (LCD Driver) | $V_{DD} - V_0$                      | -            | 25.0  | V    |

| 3. | Operating Temperature             | T <sub>op</sub>                     | Refer p      | age 3 | °C   |

| 4. | Storage Temperature               | T <sub>st</sub>                     | Refer page 3 |       | °C   |

#### 5.0 Electrical characteristics

| NO | ITEM                                     | SYMBOL            | CONDITION                                      | MIN                  | TYP | MAX         | UNIT |

|----|------------------------------------------|-------------------|------------------------------------------------|----------------------|-----|-------------|------|

| 1. | Power Supply voltage (Logic)             | $V_{DD} - V_{SS}$ | -                                              | 4.5                  | 5.0 | 5.5         | V    |

| 2. | Power Supply voltage (V <sub>LCD</sub> ) | $V_{DD}$ - $V_0$  | 25°C                                           | 22.8±5%              |     | V           |      |

| 3. | Input Voltage                            | $V_{\mathrm{IH}}$ | -                                              | $0.8V_{\mathrm{DD}}$ | 1   | $V_{DD}$    | V    |

|    |                                          | $V_{IL}$          | -                                              | 0                    | -   | $0.2V_{DD}$ | V    |

| 4  | Current Supply                           | $I_{DD}$          | $V_{DD} - V_{SS} = 5V$ $V_{DD} - V_{SS} = 30V$ |                      | 9.0 |             | mA   |

|    |                                          | $I_{\mathrm{EE}}$ | $V_{SS} - V_{EE} = 25V$                        | -                    | 8.3 | -           |      |

#### 5.1 Backlight Options

| NO | COLOR        | FORW | FORWARD VOLTAGE (V) |     |     | ARD CU<br>(mA) | RRENT | MIN<br>BRIGHTNESS |  |

|----|--------------|------|---------------------|-----|-----|----------------|-------|-------------------|--|

|    |              | Min  | Typ.                | Max | Min | Typ.           | Max   | (cd/m2) *         |  |

| 1. | CCFL - White | 280  | 340                 | 400 | -   | 5.0            | 7.0   | 600               |  |

| 2  | LED - White  |      | 5.0                 |     | _   | 90             | 120   | 500               |  |

\*Note: 1. Brightness measured at backlight surface.

2. On LCD surface, brightness is only about 10% to 15% of backlight brightness.

3. Lifetime of LED backlight 20k hrs. (CCFL = 10K hrs)

#### 6.0 Environmental requirements

| NO | ITEM                | CONDITION                                                     |

|----|---------------------|---------------------------------------------------------------|

| 1. | Operating           | Refer page 3                                                  |

|    | Temperature         |                                                               |

| 2. | Storage Temperature | Refer page 3                                                  |

| 3. | Operating Humidity  | 5% to 95%RH                                                   |

| 4. | Cycle Test          | 0°C @ 30 min to 50°C @ 30min for 1 cycle<br>run for 10 cycles |

| 5. | Lifetime            | 50000 HOURS (excluding backlight)                             |

#### Note:

- 1. The background on LCD has the possibility to be changed in different temperature range.

- 2. CCFL backlight can only function at 0°C to 50°C.

#### 7.0 LCD specification

7.1 Electro-optical characteristics (at ambient temperature =  $25^{\circ}$ C)

|                 |                          |                           |                                      |           |             | ]                     | LCD TYI            | PE .                |                             |                            |       |

|-----------------|--------------------------|---------------------------|--------------------------------------|-----------|-------------|-----------------------|--------------------|---------------------|-----------------------------|----------------------------|-------|

| NO              | ITEM                     | SYMBOL                    | CONDITION                            | STN<br>YG | STN<br>GREY | STN -VE BLUE/ PURP LE | FSTN<br>+VE<br>B/W | FSTN<br>-VE<br>BLUE | FSTN -<br>VE<br>TRUE<br>B/W | FSTN<br>-VE<br>TRI<br>AXIS | REF.  |

| 1               | Operating Voltage (Volt) | $V_{LCD}$                 | $\theta = 0$ $Cr = max$              | 22.8 ± 5% |             |                       |                    |                     | 7.1.1                       |                            |       |

| Viewing 2 Angle | θ x 1                    | GD . A                    | +20                                  | +15       | +35         | +20                   | +35                | +30                 | +40                         |                            |       |

|                 | θ x 2                    | $CR \ge 2$<br>$V_{LCD} =$ | -20                                  | -15       | -35         | -20                   | -35                | -35                 | -40                         | 7.1.2                      |       |

| 2               | (Deg)                    | θу 1                      | V <sub>LCD</sub> – 22.8V             | -25       | -20         | -30                   | -25                | -30                 | -30                         | -50                        | 7.1.2 |

|                 | (208)                    | θу2                       | 22.0 1                               | +25       | +20         | +30                   | +25                | +30                 | +30                         | +30                        |       |

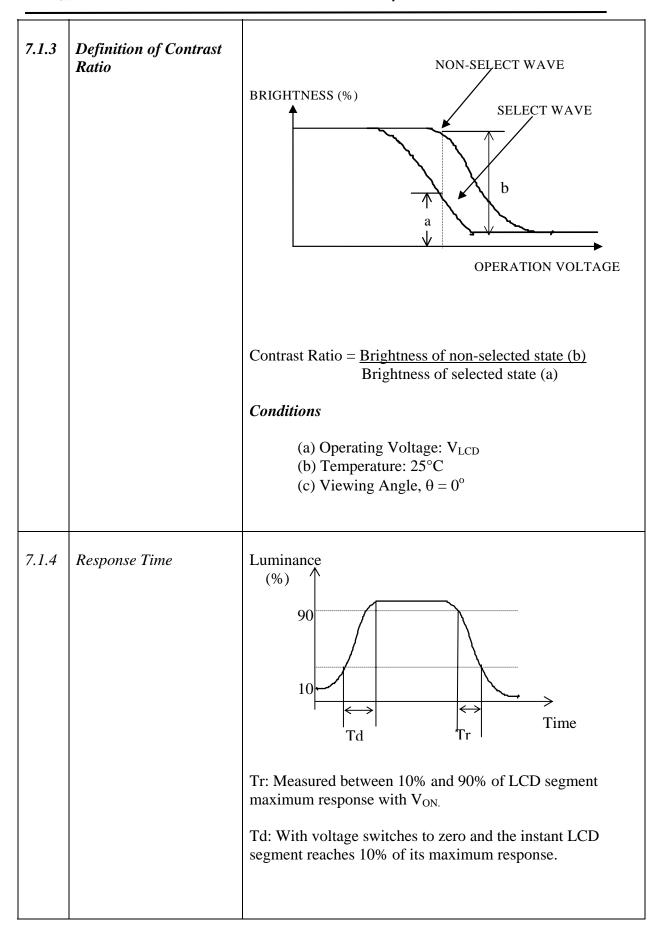

| 3               | Contrast<br>Ratio        | CR                        | $\theta = 0^{0}$ $V_{LCD}$ $= 22.8V$ | 2.5       | 2.0         | 5.5                   | 2.5                | 5.5                 | 15                          | 15                         | 7.1.3 |

|                 | Response                 | Rise<br>Time<br>(Tr)      | $\theta = 0^0$                       |           |             |                       | 400                |                     |                             |                            | 7.1.4 |

| 4               | 4 Time (msec)            | Decay<br>Time<br>(Td)     | $\theta = 0_0$                       |           |             |                       | 400                |                     |                             |                            | 7.1.4 |

#### Note:

- 1. Viewing angle data is based on bottom view product by default. Should it be a top view product, values are then swap.

- 2. Contrast ratio is based on typical data when using white colour as backlight.

- 3. Equipment Used Eldim; Ez Contrast 120R, Spot Size = 2mm

| NO    | CHARACTERISTICS                             | <u>DEFINITIONS</u>                                                                 |

|-------|---------------------------------------------|------------------------------------------------------------------------------------|

| 7.1.1 | Definition of Operating Voltage $(V_{LCD})$ | $V_{LCD}$ $V_{LCD}$ : Operating Voltage F: Frame Frequency                         |

| 7.1.2 | Definition of Viewing<br>Angle              | TOP  θ REAR  FRONT  BOTTOM                                                         |

|       |                                             | REAR ( $\theta$ y2)  LEFT( $\theta$ x2)  RIGHT( $\theta$ x1)  FRONT ( $\theta$ y1) |

#### 8.0 Interface

| 8.1     | Display Controller  | S1D13700F00                                                    |

|---------|---------------------|----------------------------------------------------------------|

| 8.2     | Display driver      | S6B2086                                                        |

| 8.3     | Cycle duty          | 1/240                                                          |

| 8.4     | Pin-out Assignments |                                                                |

| CONNECT | TOR (CN1)           |                                                                |

| Pin No  | Symbol              | Function                                                       |

| 1       | A0                  | Data type selection                                            |

| 2       | CS                  | Chip select (active low)                                       |

| 3       | D0                  |                                                                |

| 4       | D1                  |                                                                |

| 5       | D2                  |                                                                |

| 6       | D3                  | Bi-directional Data Bus. Data Transfer is performed once, thru |

| 7       | D4                  | DB0 to DB7, in the case of interface data length is 8-bits.    |

| 8       | D5                  |                                                                |

| 9       | D6                  |                                                                |

| 10      | D7                  |                                                                |

| 11      | RD                  | Active low                                                     |

|         |                     | 8080 family: Read signal                                       |

|         |                     | 6800 family: Enable clock                                      |

| 12      | WR                  | Active low                                                     |

|         |                     | 8080 family: Write signal                                      |

|         |                     | 6800 family: R/W signal                                        |

| 13      | RES                 | Reset (active low)                                             |

| 14      | A                   | Backlight power supply                                         |

| 15      | K                   | Backlight ground                                               |

| 16      | VSS                 | Ground terminal of module                                      |

| 17      | VEE                 | Negative supply for Liquid Crystal Drive                       |

| 18      | VDD                 | Supply terminal of module (+3.3V)                              |

| 19      | Vo                  | Liquid Crystal Display contrast adjust                         |

| 20      | SEL1                | 8080 or 6800 family interface select                           |

9.0 Timing Diagram For LCD Driver.

#### 9.1 Timing Characteristics for S1D13700F00

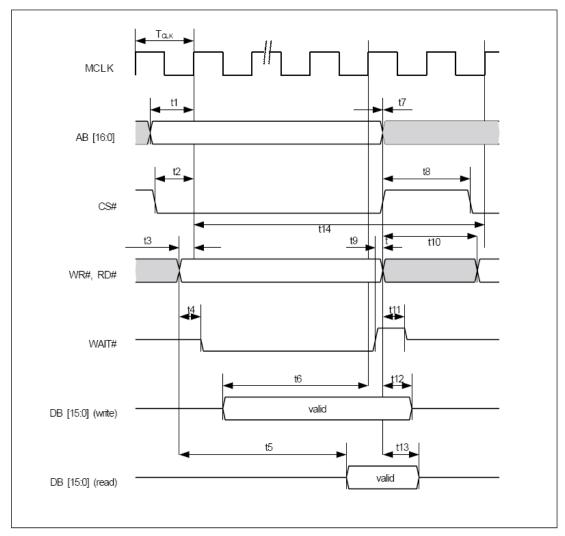

#### 8080 family interface timing:

<sup>\*</sup> MCLK denotes CLKI or the internally generated system clock.

#### Spec. No: G2432x30xxxxx REV 2.0

$[V_{SS} = 0V, V_{DD} = 4.5 - 5.5V, Ta = -40 - 85^{\circ}C]$ Spec Symbol Parameter Unit Min. Max. BUS clock frequency 64 MHz  $f_{CLK}$  $T_{CLK}$ BUS clock period  $1/f_{CLK}$ AB [16:0] setrup to first CLK rising edge where CS# = 0 and either t1 11 ns RD# = 0 or WR# = 0t2 CS# setup to CLK rising edge 9 ns RD#, WR# setup to CLK rising edge 9 t3 ns RD#, WR# state change to WAIT# driven low 5 t4 1 ns t5 RD# falling edge to DB [15:0] driven (ead cycle) 3Tc+9ns Tclk DB [15:0] setup to 4th rising CLK edge after CS#=0 and WR#=0tб 1  $T_{CLK}$ AB [16:0], CS# hold from RD#, WR# rising edge 8 t7 CS# deasserted to reasserted 1Tclk - When read ns t8 - when Write (next cycle = write cycle) 2Tclk+8ns ns - when Write (next cycle = read cycle) 5Tclk+8ns ns WAIT# rising edge to RD#, WR# rising edge 0 t9 ns WR#, RD# deasserted to reasserted 1Tclk - When read ns t10 - when Write (next cycle = write cycle) 2Tclk+8ns 5Tclk+8ns - when Write (next cycle = read cycle) ns Rising edge of either RD# or WR# to WAIT# high impedance 0.5 t11 0.5  $T_{CLK}$ TCLK t12 D [15:0] hold from WR# rising edge (write cycle) 1 ns t13 D [15:0] hold from RD# rising edge (read cycle) 1 ns Cycle Length Read 6 t14 Write (next write cycle)  $T_{CLK}$ 10 Write (next read cycle)

Spec. No: G2432x30xxxxx REV 2.0

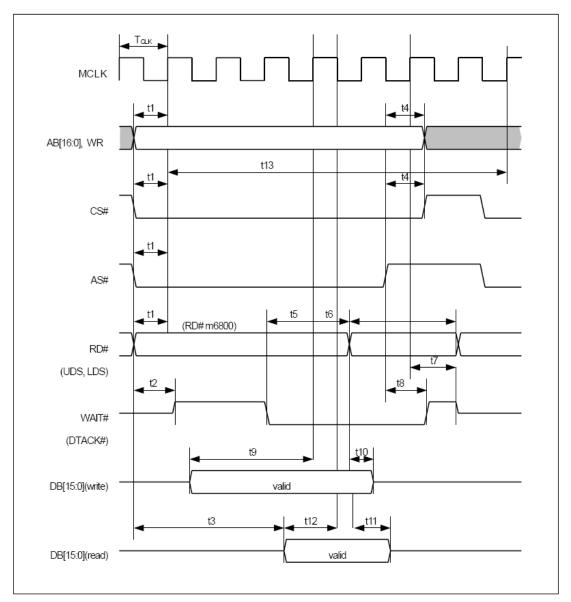

$[V_{SS} = 0V, V_{DD} = 3.0 - 3.6V, Ta = -40 - 85^{\circ}C]$

|           |                                                                                                                              | $[V_{SS} = UV, V_{DD}]$           | = 3.0 - 3.0 v, 1a = | -40 - 85°        |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------|------------------|--|

| Symbol    | Parameter                                                                                                                    | S                                 | рес                 | Unit             |  |

| Symbol    | raidilletei                                                                                                                  | Min.                              | Max.                | ] Onic           |  |

| $f_{CLK}$ | BUS clock frequency                                                                                                          | _                                 | 64                  | MHz              |  |

| $T_{CLK}$ | BUS clock period                                                                                                             | 1/f <sub>CLK</sub>                | _                   | ns               |  |

| t1        | AB [16:0] setrup to first CLK rising edge where $CS\#=0$ and either $RD\#=0$ or $WR\#=0$                                     | 12                                | _                   | ns               |  |

| t2        | CS# setup to CLK rising edge                                                                                                 | 11                                | _                   | ns               |  |

| t3        | RD#, WR# setup to CLK rising edge                                                                                            | 11                                | _                   | ns               |  |

| t4        | RD#, WR# state change to WAIT# driven low                                                                                    | 1                                 | 7                   | ns               |  |

| t5        | RD# falling edge to DB [15:0] driven (ead cycle)                                                                             | 3Tc+11ns                          | _                   | Tclk             |  |

| t6        | DB [15:0] setup to 4th rising CLK edge after CS# = 0 and WR# = 0                                                             | 1                                 | _                   | T <sub>CLK</sub> |  |

| t7        | AB [16:0], CS# hold from RD#, WR# rising edge                                                                                | 10                                | _                   | ns               |  |

| t8        | CS# deasserted to reasserted - When read - when Write (next cycle = write cycle) - when Write (next cycle = read cycle)      | 1Tclk<br>2Tclk+10ns<br>5Tclk+10ns | _                   | ns<br>ns<br>ns   |  |

| t9        | WAIT# rising edge to RD#, WR# rising edge                                                                                    | 0                                 | _                   | ns               |  |

| t10       | WR#, RD# deasserted to reasserted - When read - when Write (next cycle = write cycle) - when Write (next cycle = read cycle) | 1Tclk<br>2Tclk+10ns<br>5Tclk+10ns | _                   | ns<br>ns<br>ns   |  |

| t11       | Rising edge of either RD# or WR# to WAIT# high impedance 0.5 TCLK                                                            | _                                 | 0.5                 | T <sub>CLK</sub> |  |

| t12       | D [15:0] hold from WR# rising edge (write cycle)                                                                             | 1                                 | _                   | ns               |  |

| t13       | D [15:0] hold from RD# rising edge (read cycle)                                                                              | 1                                 | _                   | ns               |  |

| t14       | Cycle Length Read Write (next write cycle) Write (next read cycle)                                                           | 6<br>7<br>10                      | _                   | T <sub>CLK</sub> |  |

|           |                                                                                                                              |                                   |                     |                  |  |

6800 family interface timing:

<sup>\*</sup> MCLK denotes CLKI or the internally generated system clock.

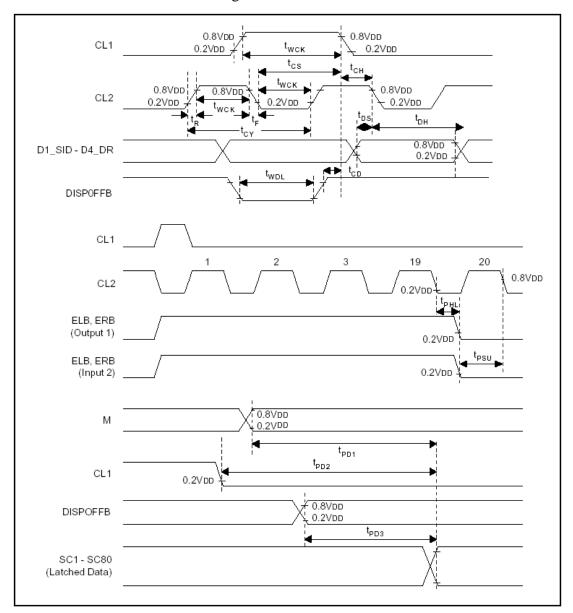

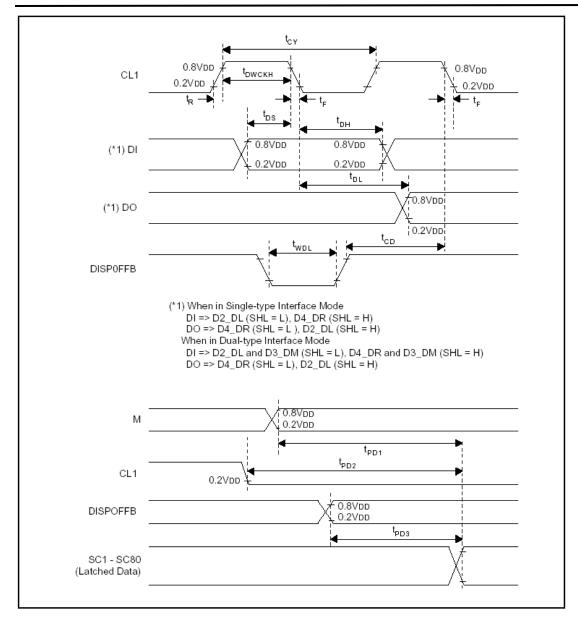

#### 9.2 LCD Driver Timing Characteristics for S6B2086

Timing Characteristic for Segment Mode

Spec. No: G2432x30xxxxx REV 2.0

$(V_{SS} = 0V, Ta = -30 \text{ to } +85^{\circ}\text{C})$

| Characteristic                        | Symbol                         | Test                  | (1) V | <sub>DD</sub> = 5V | ±10% | (2) V | <sub>DD</sub> = 3V : | ±10% | Unit |

|---------------------------------------|--------------------------------|-----------------------|-------|--------------------|------|-------|----------------------|------|------|

|                                       |                                | Condition             | Min.  | Тур.               | Max. | Min.  | Тур.                 | Max. |      |

| Clock cycle time                      | t <sub>CY</sub>                | Duty = 50%            | 125   | _                  | _    | 250   | _                    | -    | ns   |

| Clock pulse width                     | t <sub>WCK</sub>               | -                     | 45    | -                  | -    | 95    | -                    | -    |      |

| Clock rise/fall time                  | t <sub>R</sub> /t <sub>F</sub> | -                     | -     | -                  | -    | -     | -                    | 30   |      |

| Data set-up time                      | t <sub>DS</sub>                | -                     | 30    | -                  | -    | 65    | -                    | -    |      |

| Data hold time                        | t <sub>DH</sub>                | -                     | 30    | -                  | _    | 65    | _                    | -    |      |

| Clock set-up time                     | t⇔                             | -                     | 80    | -                  | -    | 120   | -                    | -    |      |

| Clock hold time                       | t <sub>CH</sub>                | -                     | 80    | -                  | _    | 120   | _                    | -    |      |

| Propagation delay time                | t <sub>PHL</sub>               | ELB Output            | -     | -                  | 60   | -     | _                    | 125  |      |

|                                       |                                | ERB Output            |       |                    | 60   |       |                      | 125  |      |

| ELB,ERB set-up time                   | t <sub>PSU</sub>               | ELB Input             | 30    | -                  | -    | 65    | -                    | -    |      |

|                                       |                                | ERB Input             | 30    |                    |      | 65    |                      |      |      |

| DISPOFFB low pulse width              | t <sub>WDL</sub>               | -                     | 1.2   | -                  | -    | 1.2   | -                    | -    | μs   |

| DISPOFFB clear time                   | t <sub>CD</sub>                | -                     | 100   | -                  | -    | 100   | -                    |      | ns   |

| M - OUT<br>propagation delay time     | t <sub>PD1</sub>               | C <sub>L</sub> = 15pF | -     | -                  | 1.0  | -     | -                    | 1.2  | μs   |

| CL1 - OUT<br>propagation delay time   | t <sub>PD2</sub>               |                       | _     | -                  | 1.0  | -     | _                    | 1.2  |      |

| DISPOFFB - OUT propagation delay time | t <sub>PD3</sub>               |                       | -     | _                  | 1.0  | -     | _                    | -    |      |

Timing Characteristic for Common Mode

Spec. No: G2432x30xxxxx REV 2.0

(V<sub>SS</sub> = 0V, Ta = - 30 to +85°C)

| Characteristic                        | Symbol                         | Test                  | (1) $V_{DD} = 5 V \pm 10\%$ |      |      | (2) V <sub>[</sub> | Unit |      |    |

|---------------------------------------|--------------------------------|-----------------------|-----------------------------|------|------|--------------------|------|------|----|

|                                       |                                | Condition             | Min.                        | Тур. | Max. | Min.               | Тур. | Max. |    |

| Clock cycle time                      | t <sub>CY</sub>                | Duty = 50%            | 250                         | -    | -    | 500                | _    | _    | ns |

| Clock pulse width                     | t <sub>WCK</sub>               | -                     | 45                          | -    | -    | 95                 | -    | -    |    |

| Clock rise/fall time                  | t <sub>R</sub> /t <sub>F</sub> | -                     | -                           | -    | 50   | -                  | _    | 50   |    |

| Data set-up time                      | t <sub>DS</sub>                | -                     | 30                          | _    | _    | 65                 | _    | _    |    |

| Data hold time                        | t <sub>DH</sub>                | -                     | 30                          | -    | -    | 65                 | -    | -    |    |

| DISPOFFB low pulse width              | t <sub>WDL</sub>               | -                     | 1.2                         | -    | -    | 1.2                | _    | -    | μs |

| DISPOFFB clear time                   | t <sub>CD</sub>                | -                     | 100                         | -    | -    | 100                | -    | -    | ns |

| Output delay time                     | t <sub>DL</sub>                | C <sub>L</sub> = 15pF | -                           | -    | 200  | -                  | -    | 250  |    |

| M – OUT<br>propagation delay time     | t <sub>PD1</sub>               |                       | -                           | -    | 1.0  | -                  | -    | 1.2  | μs |

| CL1 - OUT propagation<br>delay time   | t <sub>PD2</sub>               |                       | -                           | -    | 1.0  | -                  | -    | 1.2  |    |

| DISPOFFB - OUT propagation delay time | t <sub>PD3</sub>               |                       |                             | _    | 1.0  | _                  |      | 1.2  |    |

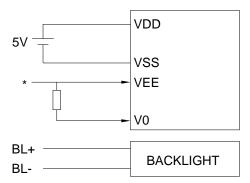

#### 10. Power Supply

- \*WITH BUILT IN DC-DC

- VEE SUPPLIED BY INTERNAL DC-DC

- \*WITHOUT DC-DC BUILT IN

- CUSTOMER NEED TO SUPPLY EXTERNAL VEE

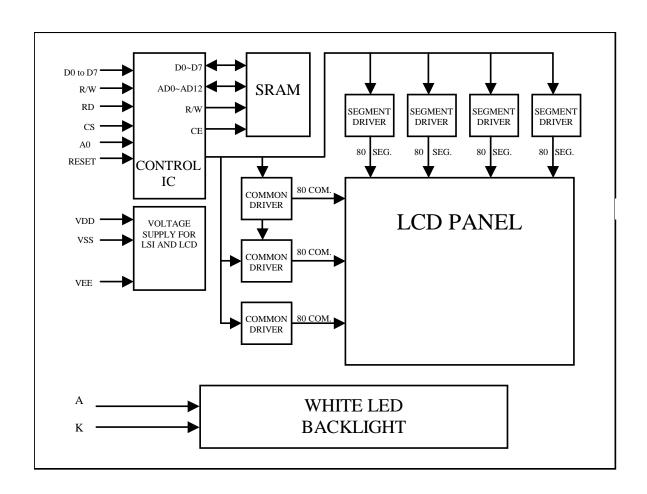

#### 11. Block Diagram

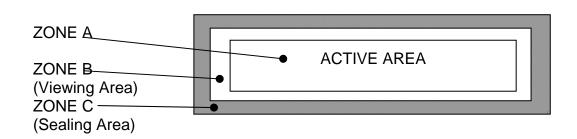

#### 12. Quality Assurance

#### 1. CRITERIA INVOLVED:

No. ITEM

1.1 Black Spot, Foreign Materials,

White Spot, Polarizer Damage

#### **CRITERIA**

Round Shape (solid figure)

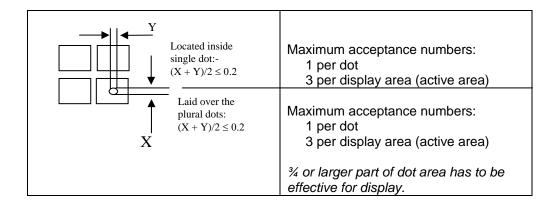

| Mean diameter = X<br>(Long axis + short axis) /2 | Maximum Acceptance Numbers |           |           |

|--------------------------------------------------|----------------------------|-----------|-----------|

|                                                  | Zone A                     | Zone B    | Zone C    |

| X ≤ 0.10                                         | Disregard                  | Disregard |           |

| $0.10 < X \le 0.15$                              | 3                          | 3         | Disregard |

| 0.15 < X ≤ 0.25                                  | 1                          | 2         | 3         |

| 0.25 < X ≤ 0.35                                  | 1                          | 1         |           |

| X > 0.35                                         | 0                          | 0         |           |

<sup>\*</sup>The 1/3 or larger parts of individual dot has to be lighted on. The solid figure is that the defect has clear-cut outline at the optimum driving condition In both positive and negative, of which size does not change when the contrast changes.

| Mean diameter = X<br>(Long axis + short axis) /2 | Maximum Acceptance Numbers |           |           |

|--------------------------------------------------|----------------------------|-----------|-----------|

|                                                  | Zone A                     | Zone B    | Zone C    |

| X ≤ 0.60                                         | Disregard                  | Disregard |           |

| 0.60 < X ≤ 0.70                                  | 3                          |           | Disregard |

| 0.70 < X ≤ 0.80                                  | 1                          |           |           |

| X > 0.80                                         | (                          | )         |           |

<sup>\*</sup> The faded figure means that the defects has unclear outline at the optimum driving condition in both positive and negative, of which size seems to change when the contrast changes.

#### 3) Linear (Fibrous)

| Siz           | e        | Maximum Acceptable No |             | e No.     |

|---------------|----------|-----------------------|-------------|-----------|

| Length        | Width    | Zone A                | Zone B      | ZoneC     |

| Disregard     | ≤ 0.03mm | Disre                 | gard        |           |

| ≤ 2mm         | ≤ 0.05mm |                       |             | Disregard |

| ≤ 1 <b>mm</b> | ≤ 0.10mm | 3                     | 3           |           |

|               | > 0.10mm | Due to (1) re         | ound defect |           |

<sup>\*</sup> Length is the whole length and width the maximum width of foreign material.

Total amount of spotting defects including round and linear:5 are the totally permissible numbers of defects in Zone A & B including above (1), (2),

(3). In case of the total permissible, the minimum distance has to be 5mm or larger between every couple of defects.

#### **APPENDIX II**

NO ITEM Pin Hole

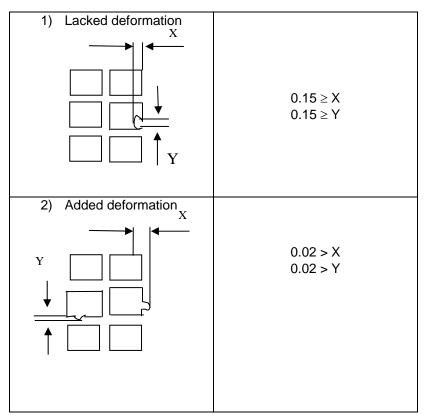

#### 1.3 Deformed display dot

|                         | Maximum Acceptable No.                          |            |               |

|-------------------------|-------------------------------------------------|------------|---------------|

| Size                    | Zone A                                          | Zone B     | Zone C        |

| D ≤ 0.30mm              | Disregard                                       | Disregard  | Disregard     |

| D <u>&lt;</u> 0.50mm    | 2                                               |            | if the        |

| 0.50 < D ≤ 0.60mm       | 1                                               | 2          | polarizer not |

| D> 0.60mm               | 0                                               |            | lifted up     |

|                         |                                                 | pealed off |               |

| Total amount of bubbles | 3 are the totally permissible numbers of bubble |            |               |

#### **REMARK**

All the other items of inspection that are not included herein must be determined by the "Limit Standard" sample, which were occasionally set up with the mutual consent of both parties. In every case of the items setup with the Limit Standard, the Limit Standard always takes precedence over the other means of definition.

Spec. No: G2432x30xxxxx REV 2.0

#### 13. Precaution for using LCM

#### 1. Liquid Crystal Display (LCD)

LCD is made up of glass, organic sealant, organic fluid and polymer based polarizers. The following precautions should be taken when handling.

- b) Keep the temperature within the range of use and storage. Excessive temperature and humidity could cause polarization degredation, polarizer peel off or bubble.

- c) Do not contact the exposed polarizer with anything harder than HB pencil lead. To clean dust off the display surface, wipe gently with cotton, chamois or other soft material soaked in petroleum benzin.

- d) Wipe off saliva or water drops immediately. Contact with water over a long period of time may cause polarizer deformation or colour fading, while an active LCD with water condensation on its surface will cause corrosion of ITO electrodes.

- e) Glass can be easily chipped or cracked from rough handling, especially at corners and edges.

- f) Do not drive LCD with DC voltage.

#### 2. Liquid Crystal Display Modules.

#### 2.1 Mechanical Considerations

LCM are assembled and adjusted with a high degree of precision. Avoid excessive shocks and do not make any alterations or modification. The following should be noted.

- a) Do not tamper in any way with the tabs on the metal frame.

- b) Do not modify the PCB by drilling extra holes, changing its outline, moving its component or modifying its pattern.

- Do not touch the elastomer connector, especially insert a backlight panel (for example, EL)

- d) When mounting a LCM make sure that the PCB is not under any stress such as bending or twisting. Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any of the elements.

a) Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels.

#### 2.2 Static Electricity

LCM contains CMOS LSI's and the same precaution for such devices should apply, namely

- a) The operator should be grounded whenever he/she comes into contact with the module. Never touch any of the conductive parts such as the LSI pads, the copper leads on the PCB and the interface terminals with any parts of the human body.

- b) The modules should be kept in antistatic bags or other containers to static for storage.

- Only properly grounded soldering irons should be used.

- d) If an electric screwdriver is used, it should be well grounded and shielded from commutator spark.

- e) The normal static prevention measures should be observed for work clothes and working benches, the latter conductive (rubber) mat is recommended.

- f) Since dry air is inductive to statics, a relative humidity of 50-60% is recommended.

#### 2.3 Soldering

- a) Solder only to the I/O terminals.

- Use only soldering irons with proper grounding and no leakage.

- c) Soldering temperature: 280°C

- d) Soldering time: 3 to 4 sec

- e) Use eutectic solder with resin flux fill.

- f) If flux is used, the LCD surface should be covered to avoid flux spatters. Flux residue should be removed afterwards.

#### 2.4 Operation

- The contras can be adjusted by varying the LCD driving voltage V0

- b) Driving voltage should be kept within specified range, excess voltage shortens display life.

- Response time increases with decrease in temperature.

- d) Display may turn black or dark blue at temperature above its operational range, this is (however not pressing on the viewing area) may cause the segments to appear "fractured".

- e) Mechanical disturbance during operation

( such as pressing on the viewing area)

may cause the segments to appear "fractured".

#### 2.5 Storage

If any fluid leaks out of the damage glass cell, wash off any human part that comes into contact with soap and water. Never swallow the fluid. The toxicity is extremely low but caution should be exercised at all the time.

#### 2.6 Limited Warranty

Unless otherwise agreed between Crystal Clear Technology and customer, Crystal Clear Technology will replace or repair any of its LCD and LCM which is found to be defective electrically and visually when inspected in accordance with Crystal Clear Technology acceptance standards, for a period of one year from date of shipment. Confirmation of such date shall be based on freight documents. The warranty liability of Crystal Clear Technology is limited to repair and/or replacement on the terms set forth above. Crystal Clear Technology will not responsible for any subsequent or consequential events.

### **Crystal Clear Technology**

16 Jalan TP5—Taman Perindustrian Sime UEP 47600 Subang Jaya—Selangor DE Malaysia